Unveiling Intel Diamond Rapids: Xeon CPUs with Distinct Core and Memory Hub Tiles

Intel is gearing up to launch its next-generation Diamond Rapids “Xeon” CPUs, which promise to bring innovative changes to the architecture. These upcoming processors are designed to enhance performance and efficiency significantly, making them a noteworthy advancement in the CPU space.

New Innovations in Xeon Architecture

The latest insights into Intel’s Diamond Rapids “Xeon” CPUs highlight the introduction of two distinct tiles: the CBB “Core Building Block” and the IMH “Integrated I/O & Memory Hub”. Unlike the Granite Rapids series, which integrated the memory controller on the same tile, Diamond Rapids will separate these components to optimize performance.

The IMH tile is expected to host up to two dies, and sources have stated that its placement will mirror that of the Clearwater Forest.

Enhanced Features and Capabilities

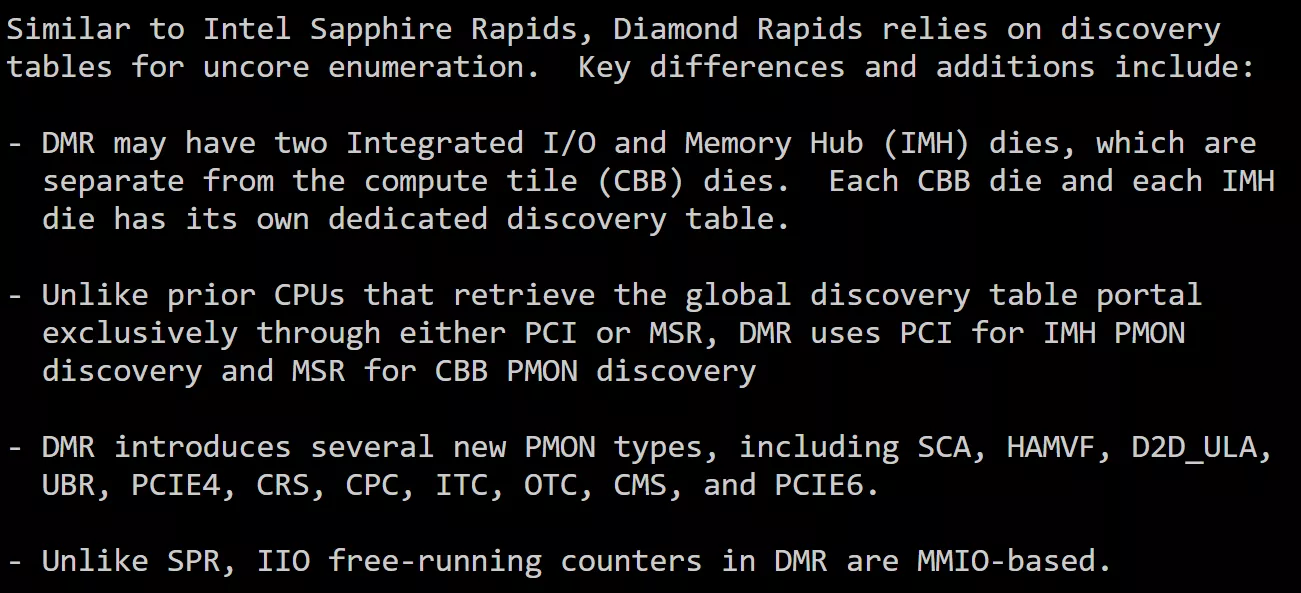

Diamond Rapids is expected to adopt new configurations in its architecture. Reports suggest that the processor will include two Integrated I/O and Memory Hub (IMH) dies, separate from the compute tiles (CBB). Each die will have a dedicated discovery table, setting it apart from previous models that used a unified system. Notably, Diamond Rapids introduces several new PMON types, such as SCA, HAMVF, D2D_ULA, UBR, and PCIE6, to name a few. Additionally, these CPUs will utilize PCIe Gen6, aligning with recent technological advancements announced in 2026.

Power and Performance Expectations

Early indicators point to impressive capabilities for the Diamond Rapids “Xeon” CPUs, with potential configurations offering up to 192 cores, and rumors suggesting even 256 cores may be possible. These CPUs will leverage Intel’s latest 18A process node and feature the Panther Cove P-Cores architecture, promising substantial performance gains. Furthermore, the LGA 9324 platform is anticipated to support up to 650W TDPs, providing robust multi-socket capabilities. Intel aims to introduce these powerful CPUs by mid to late 2026.